# Efficient Wideband High Gain Low Noise Amplifier in Modern Radars

Alaa El-Din Sayed Hafez, Mohamed Abd El-latif Mowad

**Abstract**— in this paper a wideband single stage pseudomorphic high electron mobility transistor (PHMET) amplifier has been designed at 5.8 GHz, the input and output matching circuits have a pi form.Noise cancelling principle and sensitivity analysis are performed .Simulation results have been compared with their correspondence in [10] give 2.71 dB improvement in amplifier gain at the same noise figure (N.F) and input, output returns loss. A new optimized low noise amplifier (LNA) using PHEMT at 3 GHZ have been designed to achieve an improvements of 3.3 dB in amplifier gain and 1.81 dB in noise figure.Also the two stages (common gate in cascaded with common source) LNA have been analyzed and optimized for (1-16) GHz full band application to achieve maximum gain over a wide frequency band. Simulation results carried out sever improvement in amplifier gain for the first and second structures are (3.278, 2.82) dB. The comparative study between the traditional and optimized structures showing a superior performance of LNA making them sutiable to be used in modern radar systems.

Index Terms— Pseudomorphic High Electron Mobility Transistor (PHMET), Low Noise Amplifier (LNA), Cascaded Amplifiers, Noise figure (N.F).Radar receiver.

## **1** INTRODUCTION

N the radar receiver the first stage is typically a low noise amplifier (LNA), which is designed to provide enough gain to overcome the noise effect of subsequent stages. Many researches have been introduced in complementary metaloxide-semiconductor (CMOS) area within the frequency range from 9 MHz up to 9 GHz [1-4].In the literature there are several LNA design in GaAs and bipolar technology [5-8].In this paper, a low voltage, low power and wideband PHEMT LNA at 5.8 MHz is designed and simulated using (LINC2) simulation package. As a design tool, sensitivity analysis gives a measure of sensitivity for the LNA circuit performance due to the changing of active element to be PHEMT, also assisting the radar designer in choosing the adequate circuit elements tolerances [9].Such sensitivity analysis of LNA is very beneficial in making appropriate design trade- off. Four LNA have been designed using PHEMT with two operating conditions (Q1, Q2). The first two LNA were designed using the same parameters as puplished in [10] while the second two LNA were optimized to achieve a minimum value of N.F with maximum amplifier gain.On the other side, the need of ultra wideband (UWB) circuits is steady rise for high data rate and multi-band applications. Many of (UWB) LNA have been reported with repectable performance. In UWB receiver, the LNA is realized by means of one or more (Really more than two) gain stages; therefore, the receiver noise performance depends relevantly on the N.F and the power gain of the LNA [11-12]. Many researches in wideband LNA have been provided [13-15]. Many limitions still exsists where the circuit structures on the privous studies were not optimized

Alaa El-Din Sayed Hafez, Alexandria University, Senior Member IEEE E-mail: Alaahafez @ieee.org

Mohamed Abd El-latif, Alexandria University, Member IEEE

E-mail: Turbocode\_2000@yahoo.com

for frequencies with UWB. So; LINC2 simulation package and optimizer is again used to extract the optimum design of (UWB) LNA for frequencyband ranging between (1-16) GHz.

## **2** THEORTICAL DISCRIPTION

\_\_\_\_\_

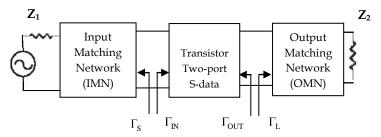

The beauty of the S-parameter amplifier design approach lies in its simplicity. The block diagram of RF amlifier is shown in figure.1.Where the active device is characterized by measured two- ports S-parameters instead of complex equivalent circuit model. It is very important to find the two terminations that satisfy our performance requirements. Restating the transducer power gain GT, [12].

$$G_{T} = \frac{\left(-\left|\Gamma_{S}\right|^{2}\right)s_{2l}^{2}\left(-\left|\Gamma_{L}\right|^{2}\right)}{\left|\left(-s_{1l}\Gamma_{S}\right)-s_{22}\Gamma_{L}-s_{12}s_{2l}\Gamma_{S}\Gamma_{L}\right|^{2}}$$

(1)

The transducer power gain is function in the source and load terminations and the scattering parameters of the two port network shown in figure.1. If the amplifier produces the maximum small-signal power gain available from PHEMT device, we must find a unique solution for two terminations to impeadnce-match both ports simultaneously. Those two terminations are named  $\Gamma_{\rm S} = \Gamma_{\rm MS}$  and  $\Gamma_{\rm L} = \Gamma_{\rm ML}$ , then,

Fig. 1. Block diagram of RF amplifier with active device charaterrized by measured two-ports S-parameters

International Journal of Scientific & Engineering Research Volume 3, Issue 7, June-2012 ISSN 2229-5518

$$\Gamma_{MS} = \Gamma_{IN}^* = \left(s_{11} + \frac{s_{12}s_{21}\Gamma_{ML}}{1 - s_{22}\Gamma_{ML}}\right)^*$$

(2)

and

$$\Gamma_{ML} = \Gamma_{OUT}^{*} = \left(s_{22} + \frac{s_{12}s_{21}\Gamma_{MS}}{1 - s_{11}\Gamma_{MS}}\right)^{-1}$$

(3)

Solving equations (2) and (3) for the two unknown  $\Gamma_{ML}$ ,  $\Gamma_{MS}$  Where (\*) is the complex conjugate gives,

$$\Gamma_{MS} = \frac{B_I - \sqrt{B_I^2 - 4|C_I|^2}}{2C_I}$$

(4)

$$\Gamma_{ML} = \frac{B_2 - \sqrt{B_2^2 - 4|C_2|^2}}{2C_2}$$

(5)

where

$$B_{1} = I + |s_{11}|^{2} - |s_{22}|^{2} - |\Delta|^{2}$$

$$C_{1} = s_{11} - s_{22}^{*}\Delta$$

$$B_{2} = I + |s_{22}|^{2} - |s_{11}|^{2} - |\Delta|^{2}$$

$$C_{2} = s_{22} - s_{11}^{*}\Delta$$

$$|\Delta| = |s_{11}s_{22} - s_{12}s_{21}|$$

Equations (4) and (5) are valid for all unconditionally stable two ports. For potentially unstable device, we define the maximum stable gain (MSG), which is highest theoretically realizable gain with passive terminations, then the device stabilized by cascaded resistance to the border line stability, that is to achieve K=1.

$$MSG = \frac{s_{21}}{s_{12}} \tag{6}$$

$$K = \frac{1 - |s_{II}|^2 - |s_{22}|^2 + |\Delta|^2}{2 - |s_{I2}s_{2I}|}$$

(7)

We can define the standing wave ratio (SWR) as the maximum Ac voltage to the minimum AC voltage in the line and is quoted at the same time as the return loss of the load. For a line terminated in  $Z_0$  the SWR is equal to one.For an open or short circuit the SWR is infinite as  $V_{min}$  is zero.

$$SWR = \frac{V_{max}}{V_{min}} = \frac{|V^+| + |V^-|}{|V^+| - |V^-|}$$

(8)

The impedance a long a transmission line can be obtained by measuring both the magnitude and phase of  $V_{total}$  using a probe inserted into a slotted transmission line. The probe usually consisted of a diode detector operating in the square law region.

The noise figure (N.F) is defined as the ratio of the total available noise power at the amplifier output to the available noise power at the output that would result only from thermal noise in the source resistance so; N.F is a measure of the excess noise added by the amplifier.

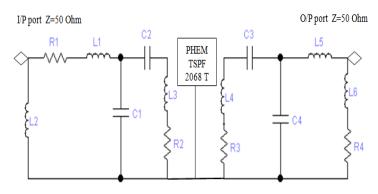

## 2.1 Single Stage PHEMT Amplifier

The LNA is considered to be a narrow band amplifier when its bandwidth is less than 20% of the center frequency. Amlifieres discussed in [13] used in a military defence systems and test equipements over require a multidecade frequency range coverage. The complete schematic diagram of LNA circuit is shown in figure .2. The PHEMT transistor used is (Sirenza Micro-device SPT-2086T). It is a PHEMT Calluim Aresenide PHEMT with Schottky barrier gate. This device is ideally baised at 3v, 20 mA for lowest noise (Q<sub>1</sub>) performance and battary powered requirments at 5v, 40 mA (Q<sub>2</sub>). The designed LNA is charactaresized in terms of S – parameters, input and output SWR, N.F and gain. On the other side a new LNA using single stage PHEMT and different circuit elements have been designed and optimized for maximum gain, minimum N.F and SWR.

Fig. 2. Schematic digram of prposed PHEMT- LNA circuit

#### 2.2 Wideband Multistage Amplifiers

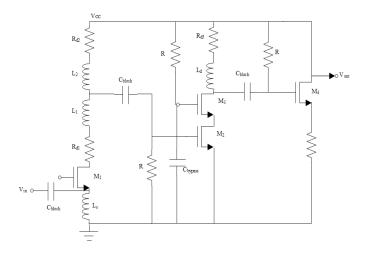

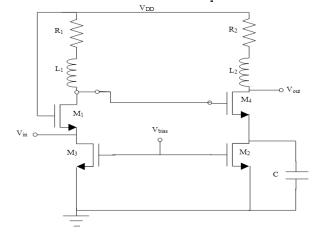

The common gate topology is well known for its constant wideband input impedance of 1/gm where gm is the trans -conductance of the transistor. The common gate topology is known to have higher noise figure than common source or cascode LNA, especially at frequencies near 10 GHz or higher [17]. Figure -3 shows the first optimized LNA consists of common gate as a first stage with cascade second stage and a buffer. Figure-4 shows the second optimized LNA. Also, the wideband input matching is accomplished using a common gate stage .The LNA gain stage is realized using a common source transistor, which is loaded by a peaked inductor R2 and L2, in order to resonate with total equivalent capacitance at drain of M2 and provide a wideband gain. Hybrid RLC tank is used (R1 and L1) to compensate all the parasitic capacitances seen from drain of M1. For the LNA a cascade topology is used with a gain switching option for bypassing a strong level of input signals at the receiver. The gain switch is implemented with the help of bypassing n type-FETs, and a high gain cascode topology. It has the inherent advantage of separating the output and input optimization criteria in the LNA circuit. The input and output matching circuits are independent of each other. Amplifiers used in military defense systems and test equipments often require multi-decade frequency range coverage. The FET transistor used is (Sirenza Micro-device ATF-36136). This 300  $\mu$ m device is ideally biased at 2V, 20 mA for lowest noise. The low noise amplifier designed is characterized in terms o S-parameters, input and output SWR, N.F and gain.

Fig. 3. Schematic circuit diagram for LNA1

Fig. 4. Schematic circuit diagram for LNA2

## **3 SIMULATION RESULTS**

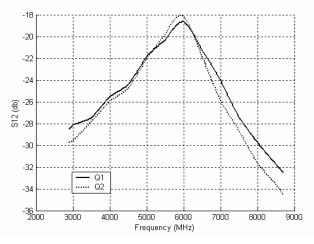

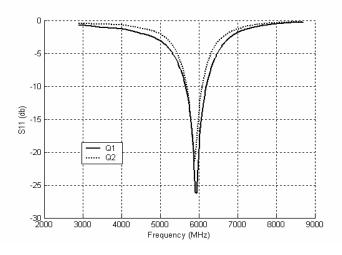

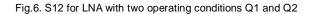

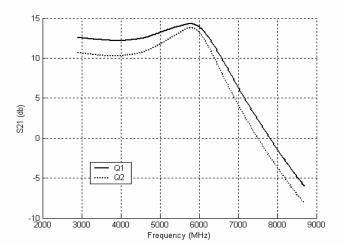

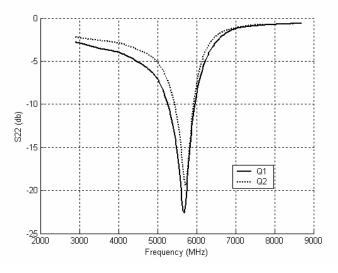

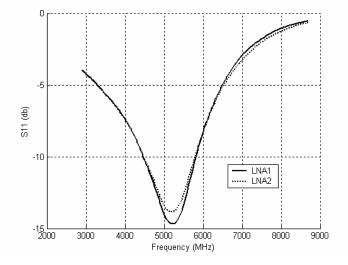

The propsed LNA have been simulated using the same parameters used in [10] ,which can be briefed in 5.8 GHz frequency with N.F equal 2.463 dB, input and output SWR of (-15.35, -16.26) dB repectively. The unique change will be replacing the active device to be PHMET instead of CMOS transistor. The amplifier scattering parameters are shown in figs 5-8. Active device replacement provides

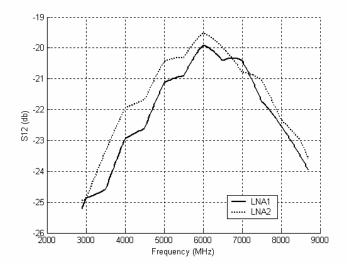

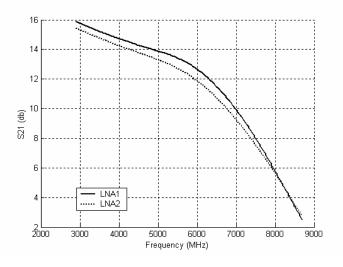

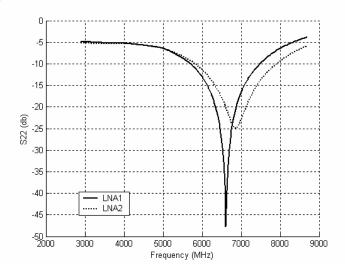

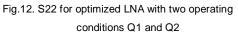

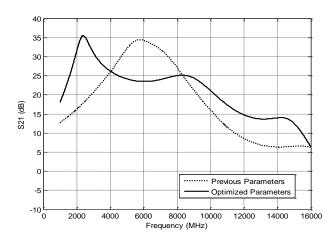

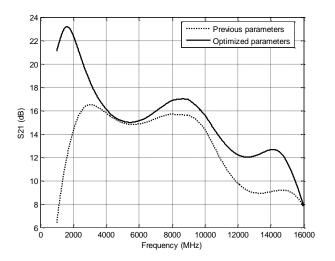

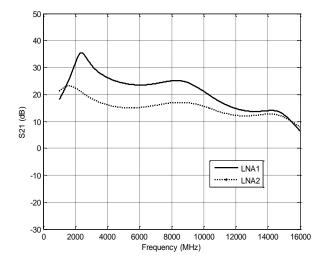

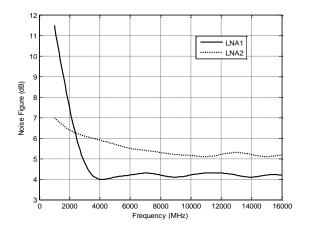

about 23.42 % improment in amplifier gain as shown in figure-7, while keeping the same value of N.F as shown in table-1. Also .The new LNA circuit using single stage PHEMT which have been designed and optimized can also be characterized using the scattering parameters as shown in figs 9-12. The amplifier gain equals 16 dB as shown in figure -11 while the N.F equals 0.65 dB at 3 GHz frequency. Additonal 3.3 dB improvement in amplifer gain have been obtained compared with PHEMT LNA gain in figure -7 at 3 GHz frequency rather than 1.81 dB enhancement in N.F.The new designed PHEMT LNA also provides the advantages of high gain over a wide frequency band since the amplifier gain is greater than 10 dB within the frequency band(3-6.8) GHz as shown in figure-11. On the other side, for wideband multistage the published LNA circuit structures [16, 17] have been simulated using schematic simulator (LINK 2) with identical components value. The first LNA circuit structure gives high gain over a wideband of frequencies from 1 to 16 GHz. The average achieved gain is 18.3 dB. Then all circuit components values are optimized to maximize the amplifier gain. The previous and optimum components values are listed in table-2. The gain achieved using the optimized parameters exceed the gain provided using the previous parameters by 15.5 % to be 21.15 dB average gain. Also the gain value of 15.3 dB has been achieved from the second optimized structure with average improvement of 18.4 %, the circuit components values are listed in table -3. Figure 13 shows the scattering parameter S21 over the whole frequency band for the first LNA circuit structure with the traditional and optimized parameters. Figure 14 shows also S21 for the second circuit structure. The two LNA are compared over a wideband of frequency, it is clear that the gain of the first structure exceeds the second one as shown in figure-15. Figure- 16 demonstrates the N.F for the two circuit structures and it is found that LNA1 have bad noise performance from 1-4 GHz with resepect to LNA2. At frequencies greater than 4 GHz, LNA1 perform the circuit structure of LNA2.

Fig.5. S11 for LNA with two operating conditions Q1 and Q2

3

IJSER © 2012 http://www.ijser.org

Fig. 7. S21 for LNA with two operating conditions Q1 and Q2

Fig. 8. S22 for LNA with two operating conditions Q1 and Q2

TABLE 1 PHEMT-CMOS LNA COMARESION

| Parameter         | Previous LNA | Present LNA   |        |

|-------------------|--------------|---------------|--------|

| Technology        | 0.18 µm CMOS | 0.25 µm PHEMT |        |

| Frequency         | 5.8 GHz      | 5.8 GHz       |        |

|                   |              | Q1            | Q2     |

| Gain (dB)         | 11.57 dB     | 14.28         | 13.8   |

| Noise Figure (dB) | 2.463 dB     | 2.463         | 2.463  |

| Input SWR (dB)    | -15.35       | -15.22        | -15.37 |

| Output SWR (dB)   | -16.26       | -16.47        | -16.18 |

Fig. 9. S11 for optimized LNA with two operating conditions Q1 and Q2

Fig.10. S12 for optimized LNA with two operating conditions Q1 and Q2

Fig.11. S12 for optimized LNA with two operating conditions Q1 and Q2

Fig.13. S21 against frequency for first LNA structure

Fig.14. S21 against frequency for second LNA structure

Fig.15 LNA gain comparesion between the two optimized structures

Fig.16. Noise fgure for both LNA structure

# PREVIOUS AND OPTIMIZED COMPONENTS VALUES FOR FIRST LNA CIRCUIT STRUCTURE

TABLE 2

| Component                                                            | Previous Values  | Optimized Values |  |

|----------------------------------------------------------------------|------------------|------------------|--|

| $\mathrm{Rd}_{1},\mathrm{Rd}_{2},\mathrm{Rd}_{3}\left(\Omega\right)$ | 10, 100, 78      | 9.43, 100, 78.1  |  |

| R <sub>1</sub> , R <sub>2</sub> (KΩ)                                 | 20K, 20K         | 20K, 20K         |  |

| $L_1, L_2, L_d, Ls (nH)$                                             | 1.8, 6.5, 2.2, 7 | 0.1, 7.76, 14.83 |  |

| C <sub>1</sub> , C <sub>2</sub> , C <sub>3</sub> (pF)                | 10,10,10         | 5, 5, 10         |  |

TABLE 3

PREVIOUS AND OPTIMIZED COMPONENTS VALUES FOR SECOND LNA CIRCUIT STRUCTURE

| Component                           | Previous Values | Optimized Values |

|-------------------------------------|-----------------|------------------|

| R <sub>1</sub> , R <sub>2</sub> (Ω) | 80,20           | 110.57, 13.65    |

| $L_1$ , $L_2$ (nH)                  | 2.2,2.5         | 10.62, 20        |

| C <sub>4</sub> (pF)                 | 10              | 17.67            |

## 4 CONCLUSION

In this paper a wideband single stage amplifier has been designed at 5.8 GHz using a PHEMT as an active device instead of CMOS amplifier.Simulation results have been compared with their correspondence in [10] give 2.71 dB improvement in amplifier gain at the same values of noise figure and input, output returns loss. A new optimized low noise amplifier (LNA) using PHEMT at 3 GHZ have been designed and optimized to achieve an addtioonal improvements of 3.3 dB in amplifier gain and 1.81 dB in noise figure. Also two stage (common gate in cascaded with common source) LNA have been analyzed and optimized in frequency band ranging between (1-16) GHz to achieve maximum gain over a wide frequency band. Simulation results carried out sever improvement in amplifier gain over the results obtained for the two structures in [16-17] respectively with no change in N.F value. The improvement values of optimized gain for the first and second structures are (3.278, 2.82) dB respectively. The comparative study between the traditional and optimized structures showing a superior performance of the designed wideband LNA making them sutiable to be used in modern radar systems.

# References

- G.Gramenga, A. Magazzu, C. Sclafani, M. Paparo, P. Erratico,"A 9mW, 900-MHz CMOS LNA with 1.05 dB-Noise Figure",26th European Solid State Conference, ESSCRIC'00, 2000.

- [2] Aleksandar Tasic, Wouter A. Serdijn and John R. Long "Matching of Low Noise Amplifiers at High Frequencies", International Symbosium on Circuits and Systems, ISCAS'03, 2003.

- [3] Abhishek Jajoo, Michael Sperling, and Tamal Muukherjee, "Synthesis of a Wideband Low Noise Amplifiers", International Symbosium on Radio Frequency Integrated Circuit (RFIC), IEEE, 2006.

- [4] Terry Yao, Michael Gordon, Kenneth Yau, M.T. Yang, and Sorin P.Voinigescu, "60-GHz PA and LNA in 90-nm RF-CMOS", International Symbosium on Radio Frequency Integrated Circuit (RFIC), IEEE, 2006.

- [5] Yuan-Kai Chu, Che-Hong Liao, and Huey-Ru Chuang," 5.7 GHz 0.18 Micro m CMOS Gain-Controlled LNA and Mixer for 802.11a WLAN Applications", 2003 IEEE Radio Frequency Integrated Circuits (RFIC) Symposium, Philadelphia, PA, 2003.

- [6] Hau-Yiu Tsui, and Jack Lau,"A 5 GHz 56 dB Voltage Gain 0.18 Mi cro m CMOS LNA with Built-in Tunable Channel Filter for DirectConversion 802.11 Wireless LAN Reciever", 2003 IEEE RadioFrequency Integrated Circuits (RFIC) Symposium, Philadelphia, PA,2003.

- [7] Pingxi Ma, Marco Racanelli, Jie Zheng and Marion Knight,"A1.4 mA& 3 mW, SiGe90, BiFET Low Noise Amplifier for Wireless Portable Applications", 2003 IEEE Radio Frequency Integrated Circuits (RFIC) Symposium, Philadelphia, PA, 2003.

- [8] M. Kumarasamy Raja, Terry Tear Chin Boon, K. Nuntha Kumar and Wong Sheng Jau, "A Fully Integrated Variable Gain 5.75-GHz LNA with on chip Active Balun for WLAN", 2003 IEEE Radio Frequency Integrated Circuits (RFIC) Symposium, Philadelphia, PA, 2003.

- [9] MouShouxian, Ma Jian-Guo, Yeo Kiat Seng, and Do Manh Anh, "A Modified Architecture used for Input Matching CMOS Low Noise Amplifiers", IEEE transaction on circuits and systems, Vol. 52, No. 11November, 2005.

- [10] Xuezhen Wang and Robert Weber,"Design a CMOS Low Noise Amplifier (LNA) at 5.8 GHz and its sensitivity analysis", 11th NASA Symbosium, 2003.

- [11] Jarkko Jussila, and Pete Sivonen,"A 1.2-V Highly Linear Balanced Noise-Cancelling LNA in 0.13µm CMOS", IEEE Journal of Solid State Circuits, Vol.43, No. 3, March 2008.

- [12] Wei-Hung Chen, Gang Liu, Boos Zdravko and Ali M. Nikjad, "A Highly Linear Broadband CMOS LNA Emplying Noise and Distortion Cancellation", IEEE Journal of Solid State Circuits Vol. 43, No. 5, May 2008.

- [13] Zhang Wei, Zhang Wan-rong, Xie Hongun, He Li-jian, Wang Yang, and Yong-Ping, "A 1-4GHz LNA for Convenient Cascade Application", Microwave and Millimeter Wave Technology, 2007, ICMMT'07, International Conference, Builin, 18-21 April, 2007.

- [14] Yang Wei-ming, He Li-ping, Yang Bin, Xie Wan-bo Shi Chen, and Chen Jian-Xin, "The Design of 3.6 GHz 4.2 GHz Low Noise Amplifier", Microwave, Antenna, Propagation and EMC technologies for wireless communications, 2007 International Symposium on, Hangzhou, 16-17 Aug. 2007.

- [15] Taris T. Begueret, and J.B. Deval. Y,"A Low Voltage Current Reuse LNA in a 130 nm CMOS technology for UWB applications", Microwave Conference, 2007, European, Munich, 9-12 Oct. 2007.

- [16] Yona Shim, Chang-Wan Kim, Jeongseon Lee, and Sang-Gug Lee,"Design of Full Band Common Gate LNA", IEEE Microwave and Wireless Components Letters, Vol. 17, No.10, Oct. 2007.

- [17] Francesco Barale and Domenico Zito,"UWB 3.1-10.6 GHz CMOS LNA", Microelectronics and Electronics Conference, 2007, RME, PhD. Research in, Bordeaux, 2-5 Jul. 2007.